1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

3. Rangkaian Simulasi [Kembali]

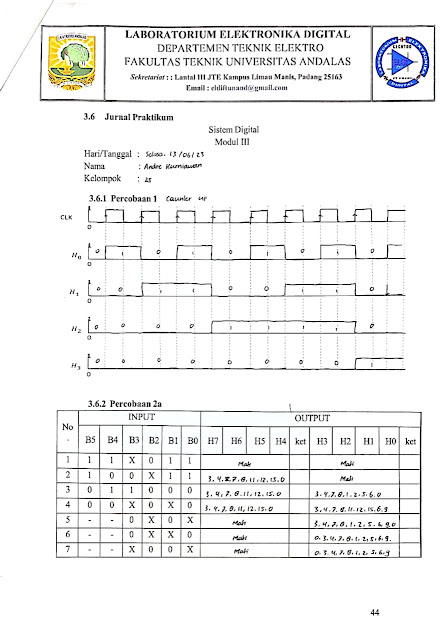

Percobaan 2a

4. Prinsip Kerja Rangkaian [Kembali]

Percobaan 2a

Pada rangkaian pertama terdiri dari IC 74LS90 dimana kaki CKA dan CKB dihubungkan menjadi satu dengan sinyal Clock, dan 4 buah kaki input dihubungkan ke SW-SPDT. IC 7493 dimana kaki CKA dan CKB dihubungkan menjadi satu dengan sinyal Clock yang sama dan 2 buah kaki input dihubungkan ke SW-SPDT.

Berdasarkan tabel kebenaran dari IC 74LS90 atur kaki inputnya menjadi kondisi Count, sehingga sistem akan menghitung, namun dalam urutan acak atau random. begitu juga IC 7493 atur inputnya menjadi kondisi Count, sehingga sistem akan menghitung, namun dalam urutan acak atau random. Hal ini disebabkan karena CK A dan B berada dalam output yang berbeda. Perubahan bilangan biner yaitu ketika sinyal clock dalam kondisi fall time.

Percobaan 2b

Pada rangkaian kedua terdiri dari IC 74LS90 dimana kaki CKA dan CKB dihubungkan ke sinyal Clock, CK B dihubungkan ke Output Q0 dan 4 buah kaki input dihubungkan ke SW-SPDT. IC 7493 dimana kaki CKA dan CKB dihubungkan ke sinyal Clock, CK B dihubungkan ke Output Q0 dan 2 buah kaki input dihubungkan ke SW-SPDT.

Berdasarkan tabel kebenaran dari IC 74LS90 atur kaki inputnya menjadi kondisi Count, sehingga sistem akan menghitung berurutan. begitu juga IC 7493 atur inputnya menjadi kondisi Count, sehingga sistem akan menghitung berurutan. Hal ini disebabkan karena CK A dan B dalam sistem yang sama, karena CKB dihubungkan ke output Q0. Perubahan bilangan biner yaitu ketika sinyal clock dalam kondisi fall time.

1. Analisa kenapa output percobaan 2a mengcounter tidak beraturan?

Jawab :

Output percobaan 2a mengcounter tidak beraturan karena CKA dan CKB memiliki output tersendiri. Dimana CKA outputnya Q0 dan CKB outputnya Q1, Q2, Q3. Namun kita menggabungkan output tersebut menjadi 4 bit. Hal ini tentu akan menghasilkan bilangan biner dengan counter tidak beraturan.

2. Analisa kenapa output percobaan 2b dapat mengcounter beraturan?

Jawab :

Output percobaan 2b dapat mengukur secara beraturan karena perbedaan output dari CKA dan CKB (pada percobaan 2a) diatasi dengan menghubungkan CKB ke output Q0 yang merupakan output CKA. Sehingga rangkaian kedua clock tersebut saling terhubung sesuai prinsip asynchronous counter yang dihubungkan seri, sehingga rangkaian hanya menerima satu sinyal clock saja.

3. Analisa mengapa output pada percobaan 2b pada IC 74LS90 hanya bisa mengcounter sampai 9?

Jawab:

Pada rangkaian 2b yang menggunakan IC 74LS90 akan menghasilkan bilangan biner dari 0 sampai 9, karena IC tersebut digunakan untuk Binary Coded Decimal (BCD) Counter yang akan mereset ke 0000 ketika output telah 1001. Hal ini terjadi karena pada rangkaian dalam IC tersebut untuk flip flop MSB, dimana kaki J dihubungkan ke gerbang AND, dan kaki K dihubungkan ke kaki Output Q, sehingga output gerbang AND itu bernilai 1 setelah bilangan biner 0111 dihasilkan. dan akan mereset (kondisi 0000), setelah bilangan biner 1001 kondisi sinyal clock fall time dihasilkan.

4. Analisa kenapa output pada percobaan 2b IC 7493 bisa mencounter sampai 15?

Jawab :

Pada rangkaian 2b yang menggunakan IC 7493 dapat menghasilkan bilangan biner 0 sampai 15 (0000-1111), karena pada rangkaian dalam IC tersebut merupakan counter JK flip flop tanpa ada kondisi pembatas seperti IC 74LS90. jenis counternya yaitu up.

7. Link Download [Kembali]

Download HTML [Klik Disini]

Download Rangkaian Simulasi [Klik Disini]

Download Video Simulasi [Klik Disini]

Download Datasheet 74LS90 [Klik Disini]

Download Datasheet 7493 [Klik Disini]

Download Datasheet SPDT [Klik Disini]

Download Datasheet Logic Probe [Klik Disini]

Tidak ada komentar: