1. Tujuan [Kembali]

a. untuk mengetahui seri-seri IC JK FF

b. mampu menjelaskan prinsip kerja seri-seri IC JK Flip Flop yang lain

2. Alat dan Bahan [Kembali]

Alat

a. Logic Probe

Logicprobe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan mengecek status logika (High atau Low) yang keluar dari rangkaian digital. Objek yang diukur oleh logic probe ini adalah tegangan oleh karena itu biasanya rangkaian logic probe harus menggunakan tegangan luar (bukan dari rangkaian logika yang ingin diukur) seperti baterai. Alat ini biasa digunakan pada IC TTL ataupun CMOS (Complementary metal-oxide semiconductor).

Logic probe menggunakan dua lampu indikator led yang berbeda warna untuk membedakan keluaran High atau Low. Yang umum dipakai yaitu LED warna merah untuk menandakan output berlogika HIGH (1) dan warna hijau untuk menandakan output berlogika LOW(0).

b. Logicstate

Logicstate

Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya.

|

| Logicprobe |

Logic probe menggunakan dua lampu indikator led yang berbeda warna untuk membedakan keluaran High atau Low. Yang umum dipakai yaitu LED warna merah untuk menandakan output berlogika HIGH (1) dan warna hijau untuk menandakan output berlogika LOW(0).

|

| Logicstate |

Bahan

3. Dasar Teori [Kembali]

Flip-flop ini dapat dianggap sebagai flip-flop universal, karena flip-flop jenis lain dapat dibuat dari flip-flop JK. Simbol logika pada Gambar 7 mengilustrasikan tiga input sinkron (J, K dan CK). Input J dan K merupakan input data, dan input clock memindahkan data dari input ke output. Diperlukan keseluruhan pulsa (bukan sekedar tansisi low ke high atau high ke low saja) untuk memindahkan data dari input ke output.

Dua sifat unik flip-flop JK adalah:1. Jika kedua data input pada keadaan nol, tidak akan terjadi perubahan pada output meskipun diberikan sinyal clock (output tetap).2. Jika kedua data input pada keadaan satu, pada tiap pulsa clock data output akan berubah dari sebelumnya (komplemen dari data sebelumnya).

Kita dapat membangun suatu flip-flop JK dari gerbang NAND. Nampak bahwa sebenarnya flip-flop JK terdiri dari dua flip-flop yang terangkai menjadi satu. Flip-flop yang kedua (slave-budak) mengikuti keadaan yang ditentukan oleh flip- flop yang pertama (master-tuan). Suatu transisi hanya dapat terjadi dengan satu pulsa clock penuh.

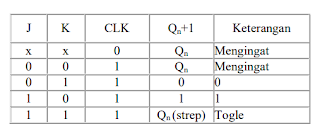

Tabel JK flip flop

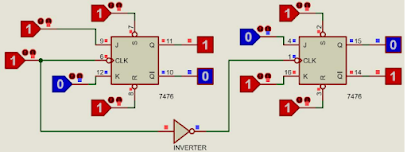

Flip-flop JK Master-Slave merupakan suatu cara lain untuk menghindari pemacuan. Flip-flop ini juga merupakan kombinasi dari 2 penahan yang diatur oleh sinyal pendetak. Flip-flop Master-Slave dibangun agar kerja JK flip-flop lebih stabil yaitu dengan menggabungkan dua buah JK flip-flop. Flip-flop pertama disebut Master dan flip-flop kedua disebut Slave. Master merupakan flip-flop yang diatur oleh sinyal pendetak pada saat naik (positif), sedangkan Slave merupakan flip-flop yang diatur oleh sinyal pendetak pada saat turun (negatif). Pada saat sinyal detak berada pada kondisi naik, Master yang aktif dan Slave menjadi tidak aktif dan sebaliknya pada saat sinyal detak pada kondisi turun, Master tidak aktif dan Slave aktif. Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output.Rangkaian aplikasi JK FF dengan input logicstate dan output logicprobe seperti gambar

Contoh rangkaian Master-Slave JK FF dengan input clock Slave JK FF dari hasil inverter clock seperti gambar dan mengganti input clock(logicstate) dengan input properti generator clock serta output(logicprobe) dengan led seperti gambar

Flip-flop ini dapat dianggap sebagai flip-flop universal, karena flip-flop jenis lain dapat dibuat dari flip-flop JK. Simbol logika pada Gambar 7 mengilustrasikan tiga input sinkron (J, K dan CK). Input J dan K merupakan input data, dan input clock memindahkan data dari input ke output. Diperlukan keseluruhan pulsa (bukan sekedar tansisi low ke high atau high ke low saja) untuk memindahkan data dari input ke output.

Dua sifat unik flip-flop JK adalah:

1. Jika kedua data input pada keadaan nol, tidak akan terjadi perubahan pada output meskipun diberikan sinyal clock (output tetap).

2. Jika kedua data input pada keadaan satu, pada tiap pulsa clock data output akan berubah dari sebelumnya (komplemen dari data sebelumnya).

Kita dapat membangun suatu flip-flop JK dari gerbang NAND. Nampak bahwa sebenarnya flip-flop JK terdiri dari dua flip-flop yang terangkai menjadi satu. Flip-flop yang kedua (slave-budak) mengikuti keadaan yang ditentukan oleh flip- flop yang pertama (master-tuan). Suatu transisi hanya dapat terjadi dengan satu pulsa clock penuh.

Tabel JK flip flop

Rangkaian aplikasi JK FF dengan input logicstate dan output logicprobe seperti gambar

Contoh rangkaian Master-Slave JK FF dengan input clock Slave JK FF dari hasil inverter clock seperti gambar dan mengganti input clock(logicstate) dengan input properti generator clock serta output(logicprobe) dengan led seperti gambar

4. Percobaan [Kembali]

A. Rangkaian

B. Prinsip Kerja

1. Jika clock bernilai rendah (0) maka flip-flop J-K master akan tidak aktif,

tetapi karena input clock flip-flop J-K slave merupakan komplemen dari

clock flip-flop master maka flip-flop slave menjadi aktif, dan outputnya

mengikuti output flip-flop J-K master.

2. Jika clock bernilai tinggi (1), flip-flop master aktif sehinga outputnya

tergantung pada input J dan K, pada sisi lain flip-flop slave menjadi tidak

aktif karena clock pemicunya bernilai rendah (0).

3. Pada saat sinyal detak berada pada tingkat tinggi, master-nya yang aktif

dan slave-nya tidak aktif.

4. Pada saat sinyal detak berada pada tingkat rendah, master-nya yang tidak

aktif dan slave-nya yang aktif.

5. Jika input J diberikan bersama-sama dengan tepi naik pulsa pemicu,

flip-flop master akan bekerja terlebih dahulu memantapkan inputnya

selama munculnya tepi naik sampai clock bernilai rendah (0).

6. Setelah clock bernilai rendah (0),flip-flop master akan tidak aktif dan

flip-flop slave bekerja menstransfer keadaan output flip-flop master ke

output flip-flop slave yang merupakan output flip-flop secara

ke seluruhan

C. Tabel Kebenaran JK Master Slave Flip-Flop

d. Video

5. File Download [Kembali]

HTML [klik disini]

Video [klik disini]

Rangkaian Simulasi [klik disini]

Data Sheet IC 7476 [klik disini]

.jpg)

.jpg)

Tidak ada komentar: